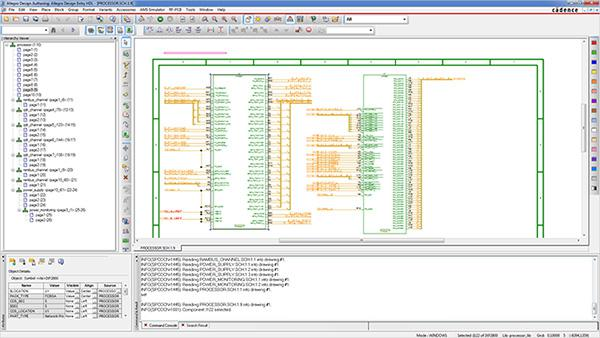

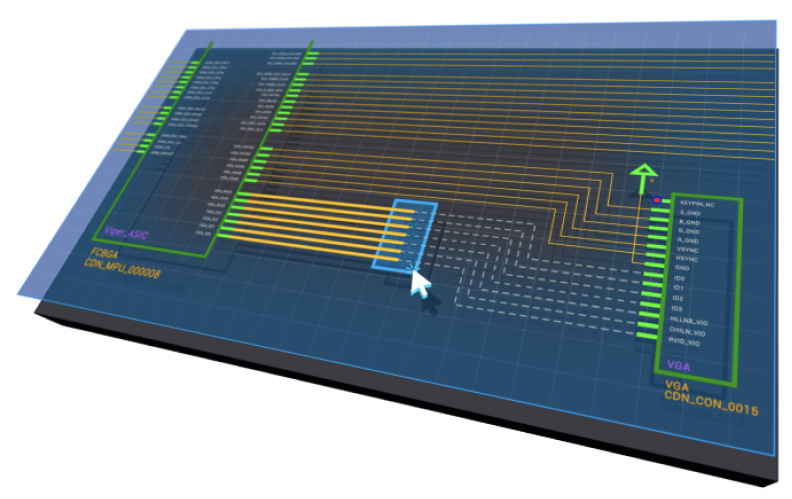

This modern schematic authoring solution is built from the ground up with multi-board systems and concurrent engineering in mind. Collaboration is seamless and secure with multi-user team design, powerful version management, and flexible access control. The tight integrations into AWR Design Environment Platform, Sigrity X Platform, electromagnetic (EM) analysis, thermal analysis, and PSpice technologies makes Allegro X System Capture the fully integrated engineering experience you’ve been waiting for.

产品详情

产品详情

This modern schematic authoring solution is built from the ground up with multi-board systems and concurrent engineering in mind. Collaboration is seamless and secure with multi-user team design, powerful version management, and flexible access control. The tight integrations into AWR Design Environment Platform, Sigrity X Platform, electromagnetic (EM) analysis, thermal analysis, and PSpice technologies makes Allegro X System Capture the fully integrated engineering experience you’ve been waiting for.

ü With fast wiring and interconnectivity, teams can manage large pin counts and complex signal handling effortlessly with net and port groups, electrical constraint sets, and smart wiring features for accurate and efficient design.

ü Integrated library and unified part search allows teams to update part and model information with ease, as well as search in your curated library network for the exact reference information necessary for your designs.

ü Built with reuse and version control in mind, Allegro X System Capture enables your engineers to customize and templatize repeatable sections to ensure that they don’t have to lay out the same pin array on several unique occasions, while allowing multi-user access and editing capabilities at both block and page levels for secure and collaborative design management.

ü Validate your electrical designs and prevent common errors with access to advanced electrical rule checks and intelligent defaults. Easily configure your design checks, parameters, and power and ground rules to meet your specific design requirements with dynamic notifications of any violations.

ü With an always up-to-date bill of materials (BOM), complete with real-time supply chain insights, electrical engineers can make data-driven decisions and keep track of the parts needed to mitigate any design risk and ensure the timely delivery of product

成功案例

成功案例