产品详情

产品详情

SiP布局选项

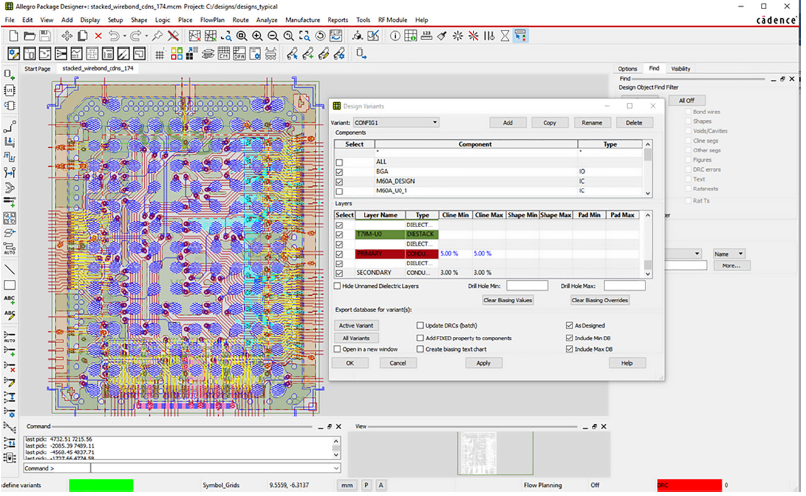

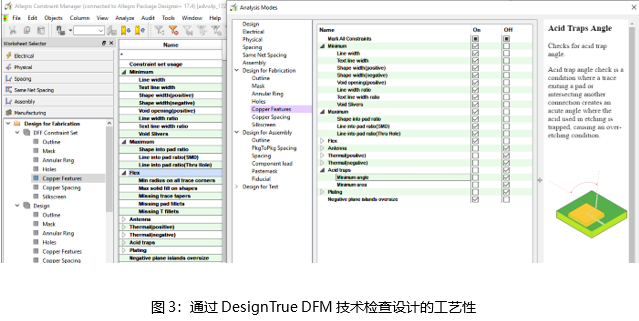

SiP布局选项增强了Cadence Allegro®X Package Designer的约束和规则驱动布局环境,以设计高性能和复杂的封装技术。其添加了一组强大的自动交互的工作流、布线和调整功能,加快了关键互连(例如,DDR存储器、高速串行、硅衬底和图形接口)的规划、优化、实例化和时序收敛。智能布线流程规划和自动分组工具减少了耗时和乏味的手动分组和布线的任务,并优化了大型总线布线,以使用最小的空间和层数。SiP布局选项还为硅基衬底添加了基于Specctra技术的额外自动布线功能。

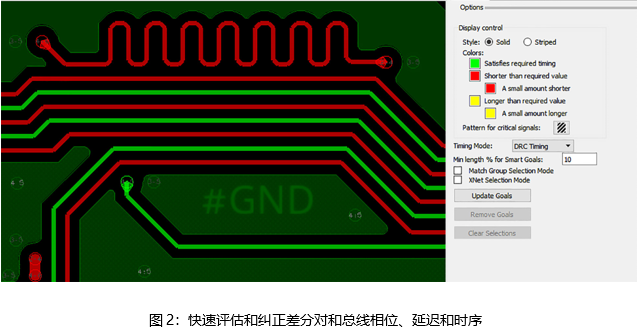

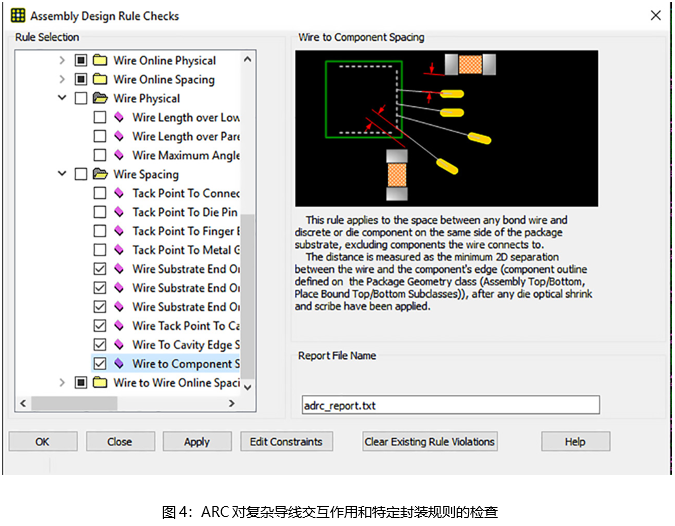

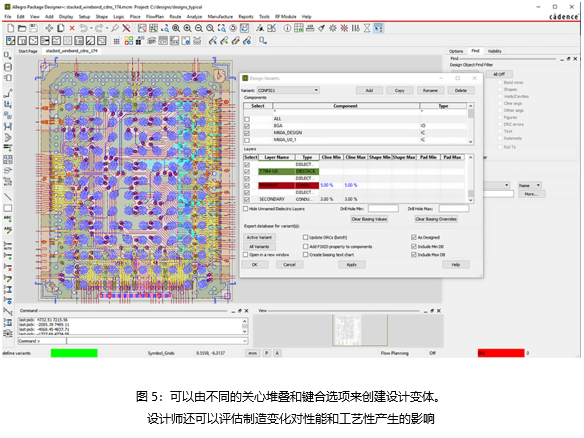

全套综合的Allegro X PCB DesignTrue DFM Technology和装配规则提高了基板产量,并防止了制造和装配的问题。该选项支持评估制造变化,并支持创建具有不同衬底堆叠、管芯堆叠和引线接合配置的设计变化,且这些配置可以由同一主设计提供。该选项还实现了与Virtuoso平台的双向流,用于IC/封装的协同设计。

优势

基于信号完整性和可布线性,允许IC、组件和基板之间的连接分配和优化,以最小化层数的使用

包含用于快速制造准备的全面基板制造设计(DFM)能力

从基础设计中创建键合和堆叠变体;评估工艺变化(如线宽)对设计规则检查和系统性能的影响

功能

接口感知设计

在高级封装设计中,为了达成产品性能、功率和带宽的要求,您可能需要转向诸如DDRx、HBM、图形和高速串行总线等协议。而您的布局工具是否能够提供快速及易用的性能,以满足设计周期的需求?那假如您可以使用分层接口感知方法来加快实现过程,并在期间提高设计质量、性能和可靠性,将会如何?

接口感知设计功能让您在更加抽象的情况下设计封装,因此可以在基于标准的界面上更快速地布线。传统的设计创作工具将总线或线束和对一组信号进行单级层次定义相结合。然而,目前的界面无法在单级层次结构中建模。其他需要解决的挑战包括了约束数量的增加、设计密度的增加、随着大引脚器件数量的增加而导致凸块和柱间距的缩小、以及布线设计的时间的增加(面对设计周期时间和资源的减少)。

为了快速方便地与接口建立连接,SiP布局选项中的分层接口感知设计功能:

通过该“工作流”,能够帮您实现包含对接口和层次网组的实例化、配置接口并将其与组件和区块进行连接、分配布局层、以及对可布线性和转义的分配进行交换的功能。

自动交互&自动布线

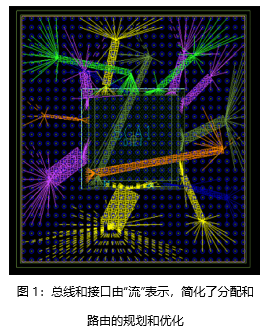

SiP布局选项增加了一整套自动交互功能,可以快速设计出包括像IC封装设计中高速接口和总线这样复杂且关键的互连。其提供了有助于规划和对模具上凸块和球型图样分组的工具。附属的工具还能解决了总线元件的时序、延迟、相位调整问题,在出现问题的地方提供了视觉警示,并提供修正问题的手段。基于Specctra的自动布线功能包含用于铸造和硅基基板。这些功能减少了繁琐、耗时、和手动的分组编辑和连接。

设计和工序变体

一个封装衬底设计通常具有多种配置,其中包括管芯构件和堆叠变化,或是管芯的接合方式。SiP布局选项允许设计师创建一个主设计,生成代表每个变体的子坐标设计,然后评估物理DRC、导线DRC、和信号完整性的不同键合和堆叠选项设计。同样的,该选项支持对DRC和信号完整性的屋里制造变体评估。

成功案例

成功案例