产品详情

产品详情

新兴的FOWLP设计的大多数一般是由无晶圆厂半导体公司的IC后端设计团队负责。然而,这些设计也对IC封装衬底设计师或团队有一定的要求——IC封装设计工具必须能够应现代FOWLP设计的要求进行扩展。通过与这新兴领域的引领者合作,Cadence开发了硅布局选件,该选件为FOWLP的特定设计和制造挑战提供了完整的设计验证流程。

由于硅布局选件使用晶圆级的实施与工艺,制造路径和典型的基于有机衬底的IC封装制造工艺是截然不同的。对于硅布局选件而言,制造工艺和IC制造工艺是相同或是非常相似的。在宏观层面上,与传统有机IC封装制造的差异和挑战包括:

l必须使用工艺设计工具包/规则平台(PDK)并进行验证复检

l特定互连(金属)必须遵循IC设计和制造中常见的铸造/制造商规则和技术

lGDSII或Stream是用于FOWLP制造的掩模创建路径

l在设计/掩膜进入制造环节前,需要进行PDK合规性验证/复检

图1 FOWLP示例

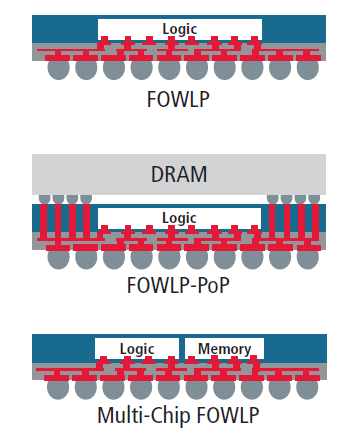

图2 对于FOWLP实现特有的一些典型设计挑战必须由设计工具和设计者

进行处理

产品功能

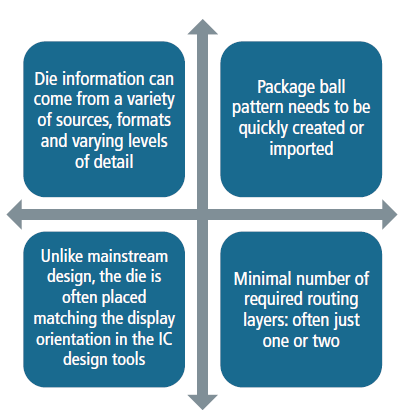

图3 金属创建和管理工具允许设计者扫描、评估和修改每一层的局部金属密度,

以满足铸造厂对铜皮和焊盘严格的制造要求

硅布局选件与Cadence物理验证系统(PVS)相结合可使设计者能够处理这些宏观层面的项目。其一些特定功能包括:

l可对金属密度进行局部化、严格控制的创建编辑工具,可对超薄封装(500至1000µm)的弯曲进行控制

l用于对网状金属和网状衬底进行跨设计平衡的金属密度实用程序

l高性能GDSII掩模处理

l选件与PVS直接集成,用于设计和掩膜的验证,并对PDK规则进行复检

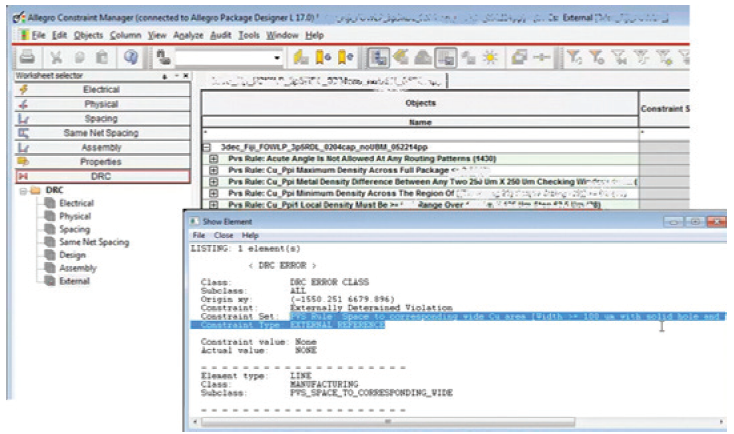

l直接在设计画布和约束管理器中报告并高亮PVS验证问题

图4 铸造厂提供的PDK/规则组驱动的PVS验证结果

通过使用约束管理器的SiP编辑器直接显示

成功案例

成功案例