概述

一些标准的高级接口如DDR3、DDR4、PCI Express、USB3.0的应用越来越广泛,一系列相关的电气规则约束就要添加到PCB设计中。

Allegro X PCB Designer通过”High-Speed”模块选项,可以快速、简单的添加一些高级接口的约束。它提供了大量的电气规则来确保PCB设计满足这些高级接口的规范。此外,还允许用户进行高速规则的扩展。

High Speed模块允许用户针对信号的拓扑来建立设计。信号的拓扑包含一些布线参数和规则,比如靠近驱动或者接收器来放置一个信号的末端电阻。如果信号的拓扑和相关的拓扑的规则不确定,规则-驱动的PCB设计系统通过规则管理器提供反馈,以便尽可能快的确保问题的解决。

High-Speed选项还支持检查信传输过程中过孔、连接器、引脚和IC 封装内部die2die内部传输时的匹配长度或者延时情况。它包含识别一段穿过挖空区域的走线(避免因回流路径引起设计迭代),支持背钻(去除孔中的多余部分,减小天线效应),通过HighSpeed设计设计环境,至少可以将关键信号时序设计的效率提高60%-70%。

产品详情

产品详情

特性

加速时序收敛

随着信号速率的增加和电源电压的降低,像DDR3,DDR4,PCIe, SATA等,PCB设计人员必须花费更多的时间来确保接口信号满足时序要求。随着PCB上器件密度的增加,努力减小时序要求误差,来确保所有信号满足时序要求,PCB设计人员需要新工具来满足日益复杂的挑战。

Timing Vision

Timing Vision是一个创新且独特的环境,允许用户直接在路由画布上以图形方式查看实时延迟和相位信息。传统上,评估路由的时间/长度的当前状态接口需要多次访问Constraint Manager和/或使用“显示元素”命令。使用嵌入式路由引擎评估复杂的时间约束和信号之间的相互依赖性一组路由信号的当前状态——通过自定义跟踪/连接线着色的DDRx字节通道或完整的DDRx接口;点画图案和自定义的数据提示信息,以最简单的方式定义延迟问题条款是可能的。通过嵌入式路由引擎,Timing Vision提供在交互式编辑期间向用户实时反馈,并增强用户开发解决大型总线或接口(如DDRx、PCIe等)上的时序问题的策略的能力。结合自动交互式相位调整(AiPT)和自动交互式延迟调整(AiDT)功能,用户可以将调谐高级接口(如DDRx)的时间加快到使用传统方法手动调谐所需时间的三分之一。

AIPT

像DDRx这样的接口中的差分对需要设计者匹配静态和动态相位。在调谐和匹配其余信号之前,对接口中的所有差分对进行相位匹配是必要的第一步。AiPT会自动匹配所选差分对的动态和静态相位。它使用一组参数,允许用户选择多个轨迹延长或缩短选项以及焊盘进入/退出选项。使用AiPT,用户可以显著缩短匹配时间差分对的静态和动态相位。

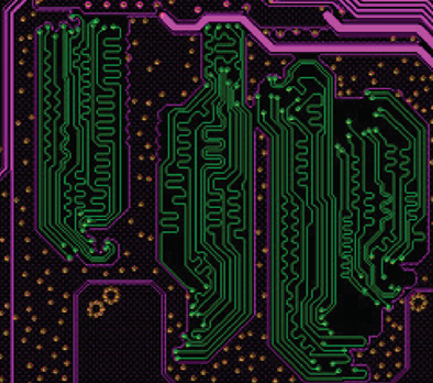

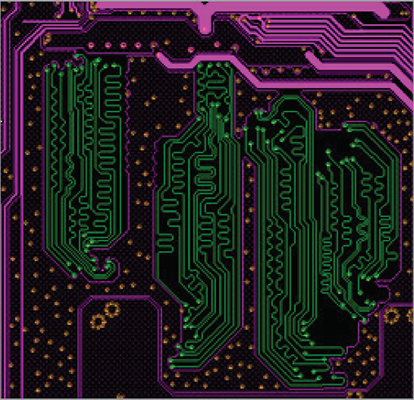

AIDT

当使用传统的手动方法时,DDRx等接口的信号延迟调谐会占用太多时间。AiDT根据用户定义的时序约束和调整参数,在用户选择的路由字节通道或接口上自动生成调整模式。AiDT计算连接所需的长度,以满足时间限制,并在添加调谐模式时使用受控推挤技术。

图1 AIDI将调谐高速信号的时间缩短了50%或更多

背钻

高速选项允许用户指定关键高速信号上的哪些过孔应回钻以避免反射。如果反向钻孔,则输出报告从底部、顶部或任何层反向钻孔NC和图例文件PCB的内芯允许用户向其PCB制造商发送反向钻孔指令。

成功案例

成功案例