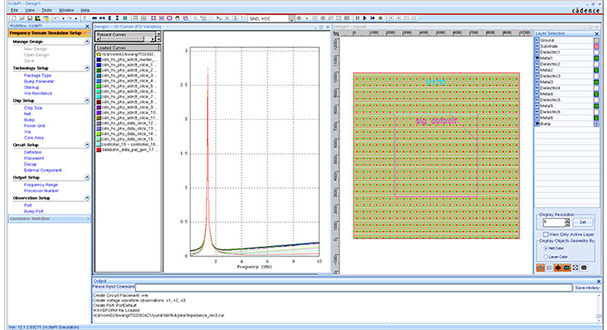

Cadence® Sigrity™ XcitePI™ Extraction technology takes chip layout data in GDSII or LEF/DEF formats, and generates a comprehensive SPICE model that consists of a fully distributed PDN and I/O nets and solvers for all electromagnetic (EM) coupling effects between signals, power, and ground. The models can be used in conjunction with models of package and boards for chip/package/board power-integrity (PI) or power-aware signal-integrity (SI) analysis.

XcitePI Extraction facilitates effective design with a range of electrical performance assessment and visualization options. These options show the impact of changes to capacitor locations, bump, pad, and power grid designs, helping design teams avoid costly late-stage design re-spins.

产品详情

产品详情

l Accurate distributed model to reflect the true circuit behavior, including TSV

l Efficient extraction of mutual inductance and coupling capacitance for both power grid structures and I/O signal interconnects

l Maximum accuracy with a compact chip model that is spatially distributed with high pin resolution

l Rapid what-if experiments for achieving targeted design performance improvement

l Compact circuit size, compressed from the model of the entire multi-layer power, ground, and/or signal connections

l Simple and easy to run at any chip design stage, even when chip is not completed

l Generates SPICE models of full-chip PDN for use in chip/package/board simulations

l Generates SPICE models of chip I/O signals coupled to power/ground to be used in chip/package/board analysis of high-speed channels and buses

l Includes MCP model header for easy connectivity to package and IBIS models

l Generated models include effects from TSVs

l Visualizes potential chip performance issues

l Assesses on-chip decoupling capacitor implementations

l What-if analysis of decap, bump, wire, and via size, and location

成功案例

成功案例