产品详情

产品详情

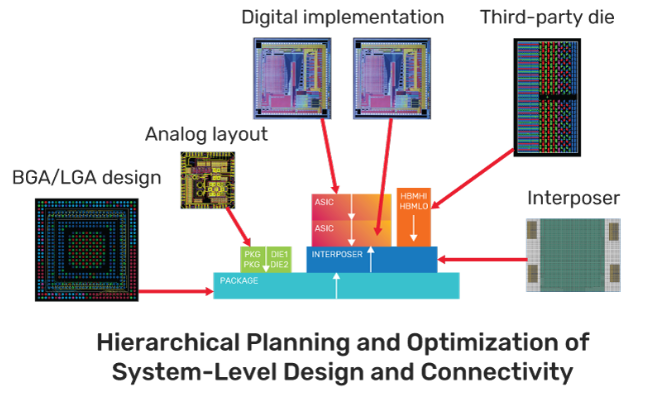

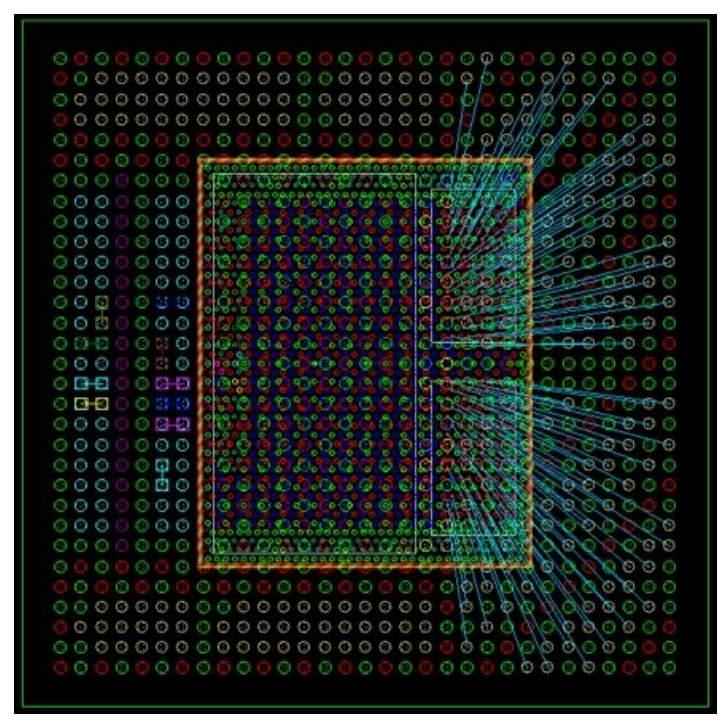

Integrity System Planner通过提供一个单一的环境来构建、评估和驱动构成系统的多个基板之间的连接,帮助设计团队优化设备和系统性能。它非常适合系统架构师、项目负责人或负责开发管芯到管芯、管芯到封装/插入器或封装到PCB接口的个人设计师,并提出凸块/球配置和信号分配的最佳组合。Integrity System Planner的一个关键区别是能够保持每个设计的单个完整性和范围,同时提供完整的系统视图和互操作性,如图1所示。每个设计都可以针对适当的实施环境进行准备和管理。系统级分析可以从Integrity 3D-IC系统平台进行配置和启动,该平台是Cadence的高容量、统一的设计和分析平台,用于设计多个小芯片。

图1 组装和管理系统设计

图1 组装和管理系统设计

关键特性

l通过构造校正单源系统设计

l优化的衬底间连接和凸块分配

l通过减少总导线长度提高性能

l通过优化的连接减少布线层和过孔

l减少ECO循环时间和复杂性

功能

系统级装配和规划

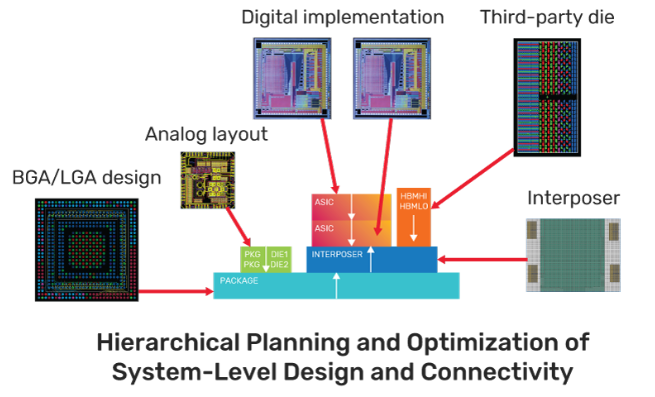

Integrity System Planner提供了一个环境,能够将来自各种来源的设计内容统一起来,用于系统级设计组装、平面布置规划、连接定义和优化(图2),并将这些数据传达给各自的实施工具以完成。它是一个整体跨衬底解决方案的一部分,该解决方案提供了一系列Cadence产品的互操作性,包括Cadence Innovus实现系统和Cadence Virtuoso Studio。此外,Integrity System Planner中开发的软件包设计可以直接导入Cadence Allegro package Designer Plus环境,以帮助加快详细的软件包实施。通过这种方式,整个系统设计可以通过单个源的实现来创建和管理。可视化系统级连接的能力与连接优化功能相结合,实现了整个系统的通气优化。

图2 系统级连接定义、可视化和优化

图2 系统级连接定义、可视化和优化

接触层定义和管理

跨衬底优化的第一步是建立管芯、封装、中介层和PCB(器件)之间的物理关系。识别来自每个设备的接触焊盘层以建立物理连接,并且可以在接触的设备上自动创建匹配的接触焊垫。Integrity System Planner自动管理这些关系,并通过设计更新维护每个基板上接触垫的完整性,如图3所示。

图3 配置设计堆栈

创建接触层还建立了设备之间的逻辑关系。作为接触焊盘定义的结果,网被自动传播到被接触的设备。网络名称前缀唯一地标识复制裸片的网络名称,例如高带宽存储器(HBM)s。然后可以映射网络以在具有不同网络名称的设备之间建立连接。

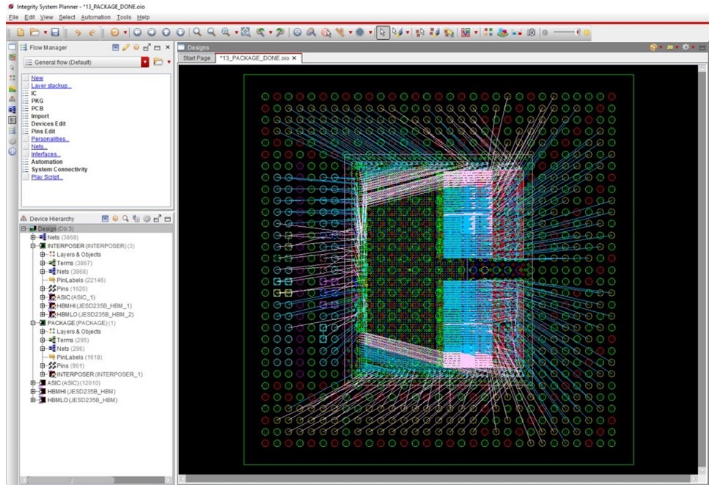

执行衬底间连接检查,如图4所示,以验证接触层的完整性。检查包括引脚接触百分比、引脚偏移、引脚数量不匹配、术语方向和网络映射。会列出违规行为,并可以突出显示违规对象。此功能有助于在整个设计过程中保持系统设计连接的完整性。

图4 基板间连接检查

连通性定义和优化

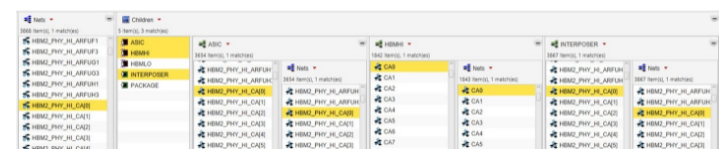

作为一种灵活的探索环境,Integrity System Planner可以使用现有网表,也可以不使用网表,或者在大多数情况下使用部分网表。网表编辑器功能允许设计者在逻辑层次结构中上下传播和映射网络,如图5所示。连通性可以通过使用正则表达式定义模式来交互式映射网络来定义。作为接触焊盘创建或连接优化过程的结果,网在基板之间自动传播。连接也可以通过导入CSV网络映射文件、CSV术语文件或Verilog网表来定义。

图5 交互式网络映射和可视化

连接优化功能可实现自动引脚分配,以减少路线交叉和净长度。如图6和图7所示,此功能可用于优化管芯连接或顶侧凸块/焊盘到底侧凸点/焊球。

图6 Die-to-die连接优化

图7 优化底部凹凸分配

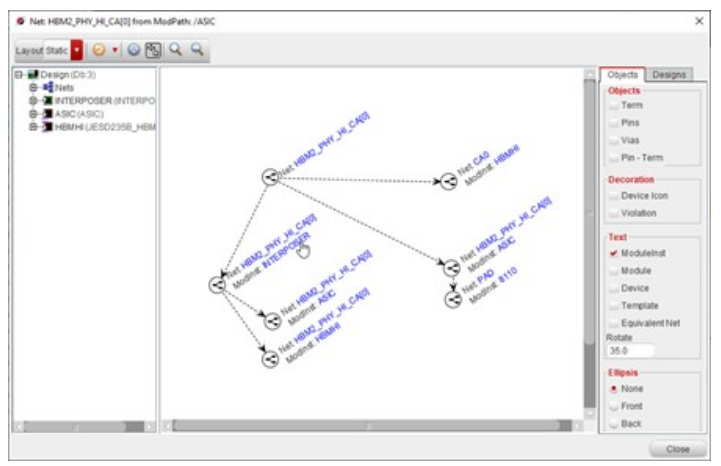

可以使用“网表编辑器”功能或“网络图”功能分析系统级连接。Net Graph显示了网络的整个拓扑结构,包括映射的子网络名称、术语、引脚和网络上存在的过孔,如图8所示。

图8 探索整个系统设计中的网络拓扑

实施集成

Integrity System Planner与Allegro Package Designer Plus完美集成。数据库直接导入Allegro Package Designer Plus,以生成实现所需的符号、层堆栈、焊盘堆栈和网表。增量更改可以在Integrity System Planner中进行,并导入到活动Allegro Package Designer Plus设计中。Allegro环境中所做的更改,如引脚交换、零件放置等,可以重新合并到Integrity System Planner源代码设计中,以保持它们的同步。

Integrity System Planner也是Integrity 3D-IC平台的驾驶舱,提供与Innovus Implementation System、Virtuoso Studio和Allegro Package Designer Plus的紧密集成。

接口格式

l芯片数据:模具摘要、库交换格式(LEF)/设计交换格式(DEF)、模具TXT和引脚CSV文件

l包数据:与Cadence Allegro(.sip,.mcm)、die TXT、pin CSV文件和die Abstract进行直接数据交换

lPCB数据:Cadence Allegro PCB(.brd)和其他流行系统

成功案例

成功案例