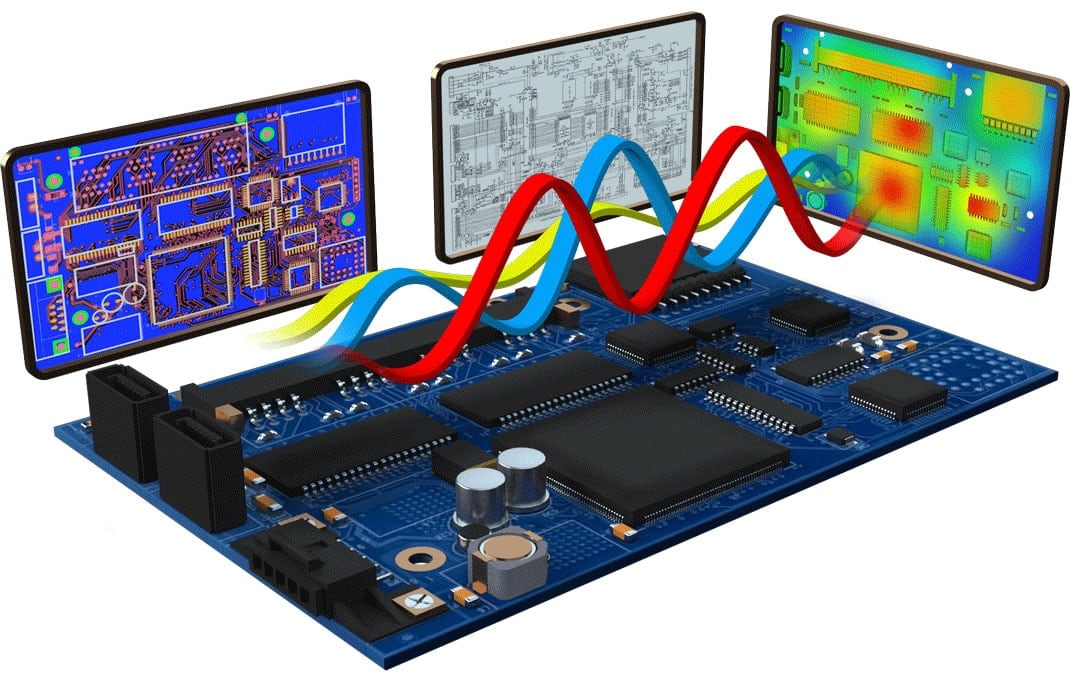

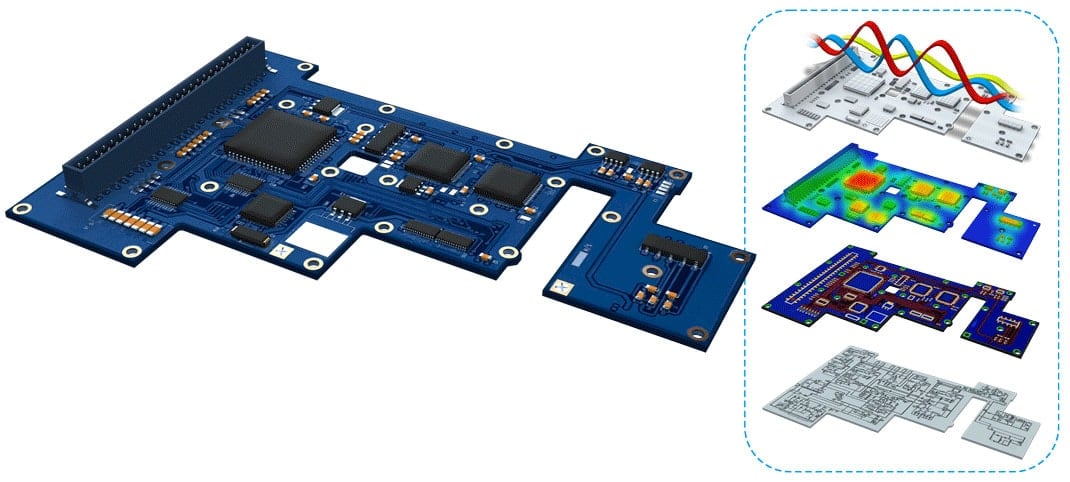

The Cadence Allegro X Design Platform is a robust and unified system design solution that facilitates a collaborative team-based environment to support cutting-edge and modern electronic design needs. Easily tackle anything from the most complex and technically demanding systems to the most routine board and circuit requirements. It offers an integrated ecosystem consisting of schematic capture, PCB layout, and in-design analysis, supported by centrally managed and versioned design data, reducing the likelihood of unnecessary design conflicts and errors.

The platform's wide range of automation features help streamline repetitive tasks, while seamless ECAD-MCAD collaboration ensures the alignment between electrical and mechanical designs. Access to real-time simulations and analyses, design for manufacturing (DFM) checks, and the shift-left methodology for early issue detection, help accelerate design cycles and improve manufacturing quality, while features for advanced routing, high-density, and Radio Frequency (RF) streamline complex design tasks. This extensible solution boosts productivity, shortens time-to-market, and ensures that your engineering teams deliver compliant, high-performance, reliable, and manufacturable multi-board systems.

产品详情

产品详情

Schematic Capture

Allegro X System Capture provides a highly integrated, automated, and collaborative workspace for the modern hardware engineer. Designed from the ground up for multi-board systems, System Capture enables everything from top-level functional diagrams all the way down through low-level circuit capture and variant management. Leveraging integrations with Cadence’s other products including PSpice, Sigrity X, Clarity 3D Solver, Celsius Thermal Solver, and AWR Microwave Office, engineers can take advantage of the electrical engineering (EE) cockpit to run electrical overstress (EOS) analysis, mean time between failure (MTBF) analysis, thermal floor planning analysis, and advanced electrical rule checks to ensure reliable and durable designs.

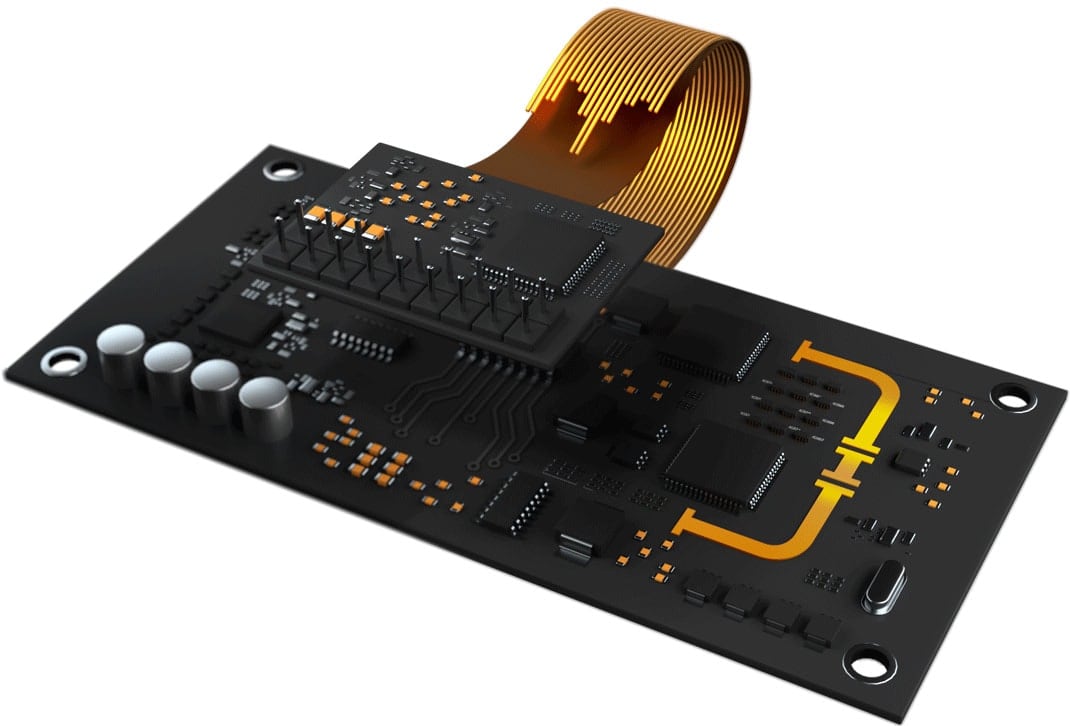

PCB Layout

Tackle simple to complex PCB designs with unparalleled efficiency and precision using the intuitive Allegro X PCB Editor, featuring a robust routing engine and constraint management system that accelerates layout creation and ensures design integrity. Advanced visualization tools provide deep insights into electrical performance, while specialized features for flex and rigid-flex designs cater to modern electronic demands. High-speed and high-voltage design challenges are met with advanced routing and tuning capabilities, z-axis aware constraints, creepage and clearance constraints, and in-design analysis capabilities, guaranteeing optimal signal and power delivery. Additionally, PCB Editor supports HDI and miniaturization, enabling designers to work on compact and complex designs optimizing board real estate. Accelerate time to market using automation and collaboration including the all-new power plane generator, design review and markup, and Allegro X Symphony team design.

Data Management

As a highly integrated and extensible data management solution, Allegro X Pulse is the foundation and framework for enabling true enterprise-level product data management (PDM). Through Pulse, users can collaborate on schematics in real-time, manage the schematic to PCB engineering change order (ECO) process, communicate natively with product lifecycle management (PLM) systems including retrieving and publishing data, as well as versioning and sharing existing projects. Out-of-the box PLM connectors include Oracle Agile, PTC Windchill, Siemens Teamcenter, Dassault Systèmes 3DEXPERIENCE and 3DEXPERIENCE WORKS. Unlike other PDM solutions, Pulse is natively integrated with the Allegro X Design Platform resulting in a true integration of files, projects, design reuse, BOM, component model data, and manufacturing deliverables. Additionally, Pulse provides a complete solution to author, verify, manage, and use the CAD library, ensuring that every element from your projects down through footprints and symbols are versioned and distributed across teams through a single sign on (SSO) enabled user-level or group-level permission control. Corporate IT can rest easy knowing Pulse utilizes the latest in high availability server architecture, including Hadoop Distributed File System (HDFS) and Zero Trust Network Access (ZTNA) ensuring stability, security, and scalability.

EE Cockpit

The electrical engineering (EE) cockpit is a powerful, integrated design environment that enhances the productivity and efficiency of electrical engineers throughout the PCB design process. The cockpit consolidates various design domains into a single, user-friendly interface, addressing the challenge of learning multiple tools and the constant context switching between them. With access to always up-to-date design data, engineers can seamlessly manage component libraries, capture functional intent, run reliability analyses, extract and analyze high-speed circuit topology, investigate power distribution, simulate analog and mixed signal, and explore critical routing and placement strategies based on thermal feedback, all within a cohesive platform. With support for advanced electrical rule checks and constraint management, it’s easy to ensure that designs meet manufacturing and performance requirements. The robust integration with other tools within the Cadence ecosystem such as AWR Microwave Office, Celsius Thermal Solver, and Clarity 3D Solver further enhances design accuracy and reliability, reducing time-to-market.

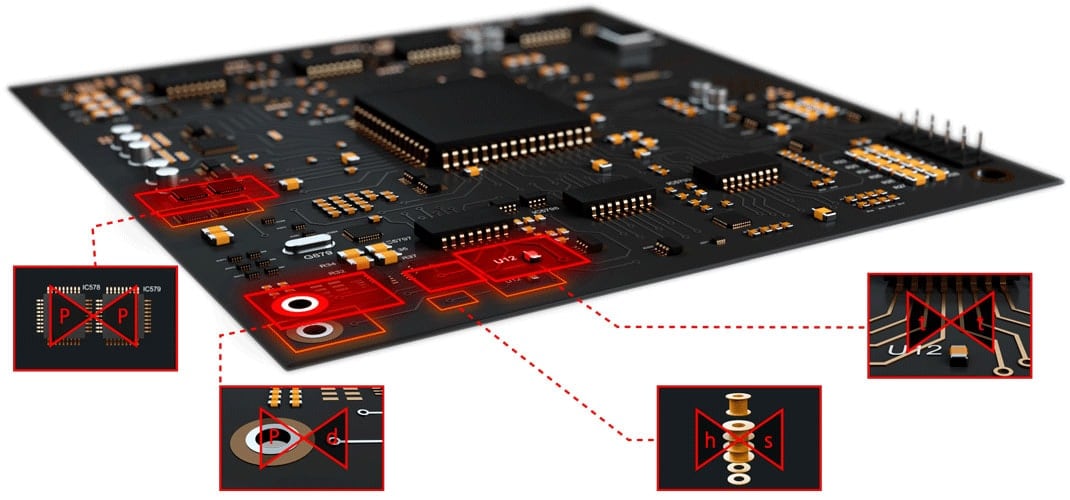

Design Reliability

Create robust and reliable designs that meet regulatory standards from the start with access to advanced electrical rule checks (ERCs), PSpice, and comprehensive analyses such as electrical overstress analysis (EOS) and mean time between failure (MTBF). Automated schematic integrity checks detect and flag issues such as connectivity, device, protocol specific, mechanical, and power net problems, removing the risk of errors that typically arise in manual reviews. EOS identifies components prone to failure, allowing for more reliable component selection and better product longevity. MTBF adheres to the Failure In Time/Duration Equivalent Standard (FIDES) and helps estimate PCB lifespan so you can evaluate if your design is able to withstand the environmental conditions it’s exposed to, such as extreme temperatures, allowing you to make informed decisions about product maintenance, replacement, and yield.

Library Management

Streamline the organization, creation, and distribution of component libraries across design teams with access to a centralized repository. With all stakeholders having access to the latest component information, it’s easy to regulate component standardization and overall design efficiency while maintaining consistency and accuracy across designs. The unified part search dashboard provides a modern, parametric search experience with access to multiple content providers, reducing the time spent searching for components. Status of new parts are easily tracked utilizing the formalized part request process, and all library models and data are version controlled providing a complete accounting of the component history. PLM integrations provide part meta data synchronization with Allegro X Pulse ensuring your corporate approved vendor list (AVL) of components and supply chain availability matches what engineers are annotating to their designs. These capabilities empower designers to create and maintain high-quality, manufacturable PCB designs efficiently, reducing errors and saving production costs. Moreover, Allegro X System Capture is compatible with Design Entry-HDL (DE-HDL) and OrCAD X Capture-based OLB libraries, ensuring continuity in design workflows.

Manufacturing

Ensure the manufacturability of your PCB designs from the start with access to DesignTrue DFM rules. Comprehensive checks for fabrication, assembly, and testing validate your designs against manufacturing constraints and standards, ensuring aspects like component placement, solder mask definition, copper trace ratios, and via types meet requirements. The constraint-driven approach mitigates potential issues by enabling DFx checks within the PCB Layout environment, facilitating quicker time-to-market and significantly reducing the risk of costly re-spins and design iterations. This solution optimizes PCB manufacturing readiness, ensuring seamless collaboration between design teams and manufacturing partners to achieve compliant and high-quality PCBs.

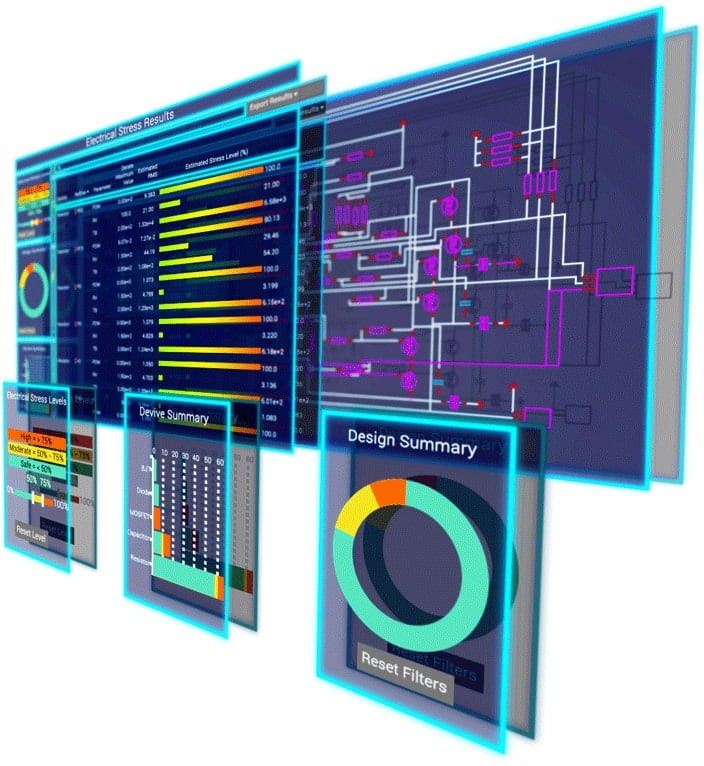

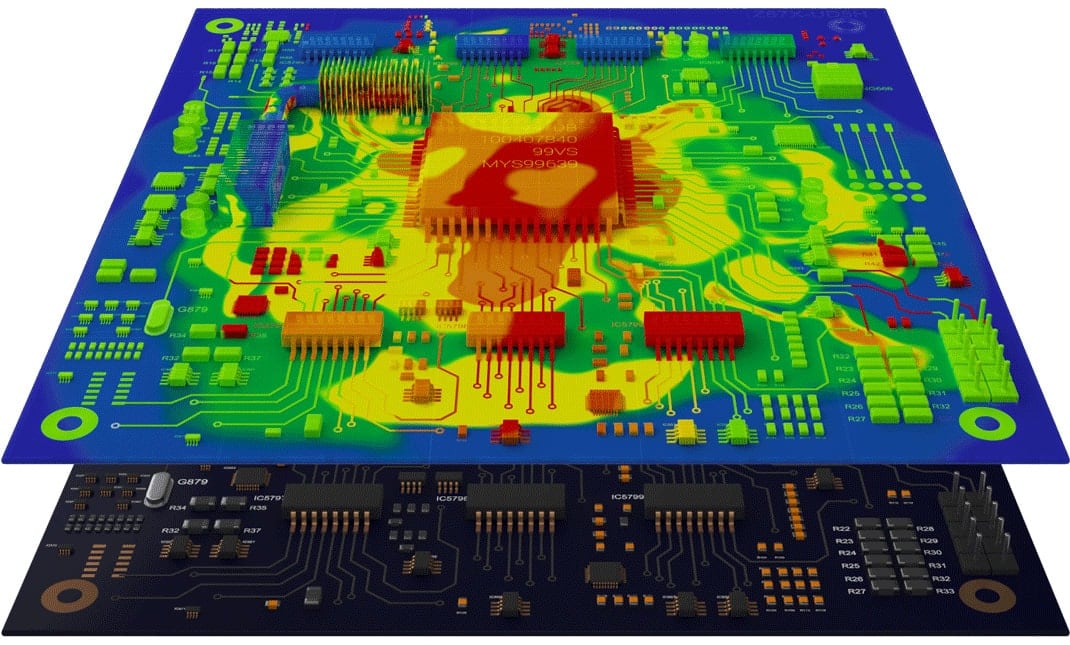

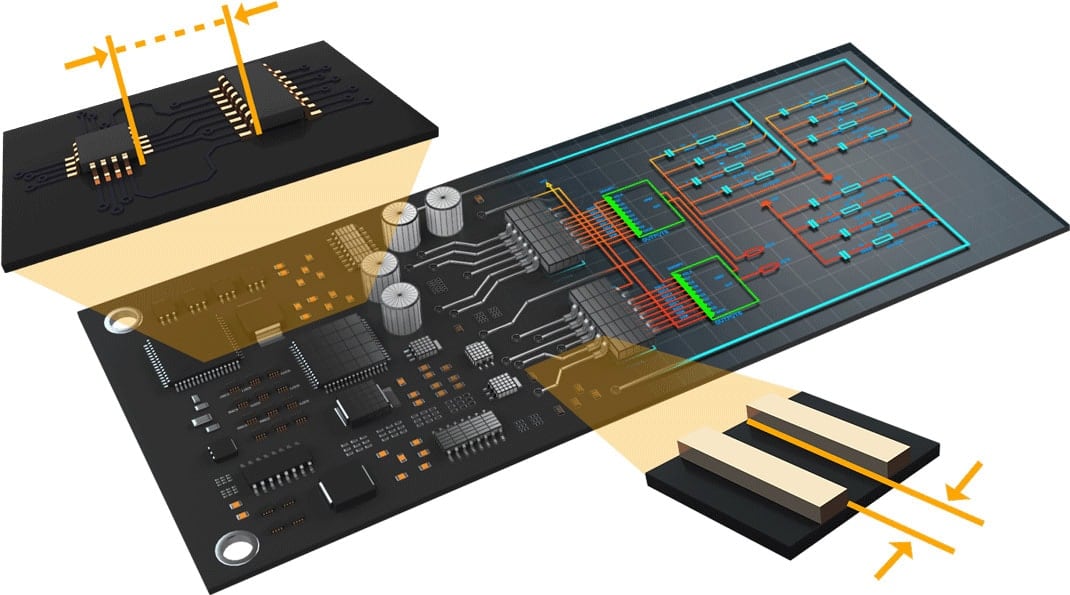

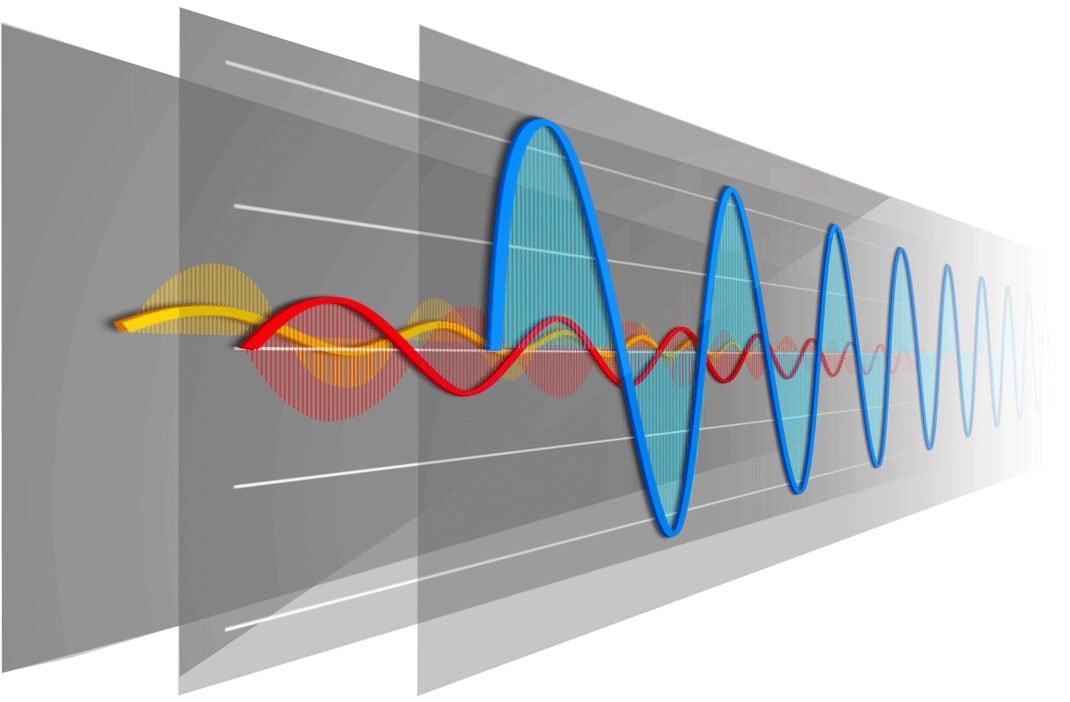

In-Design Analysis

Powered by Sigrity X technology, the in-design analysis workflows within the Allegro X Design Platform offer dynamic and color-coded in-context analysis capabilities that enable engineers and PCB designers to identify and fix potential signal and power integrity issues earlier in the design cycle enhancing design performance and reliability. With an ever-increasing list of workflows that include impedance, coupling, crosstalk, reflection, IR drop, return path, and power inductance, users can eliminate guesswork and ensure their design will function as intended. Utilize these tools to enable the real-time validation and optimization of your PCB design, while reducing the need for costly post-design corrections, ensuring that your final product meets strict performance requirements.

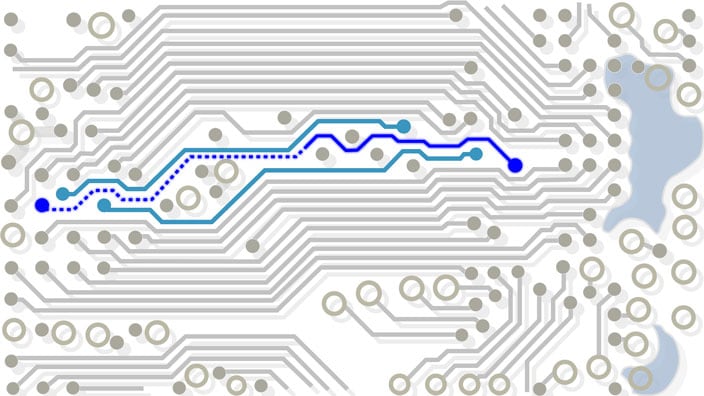

Interactive Routing

The extensive interactive routing capabilities provide PCB designers with powerful tools to efficiently and accurately route both simple and complex designs. With support for real-time constraint aware routing, group routing, auto-interactive delay and phase tuning, intelligent via management, and dynamic shape updating that adapt to your design requirements, these capabilities provide precise control over your signal integrity and timing requirements, ensuring high-performance designs. As you route, a dynamic and graphical heads-up display for high-speed constraints provides instantaneous feedback, allowing you to manage and adjust any critical high-speed signal. Multi-line routing enables the simultaneous routing of multiple traces on both rigid and flex regions, streamlining the process for densely packed boards and curved flex regions. Specialized routing methods like scribble, fiber weave, tab, snake, and automatic neck mode make impedance matching and BGA breakout a breeze. Reduce design time and maximize overall productivity while maintaining the highest standards of design quality and reliability.

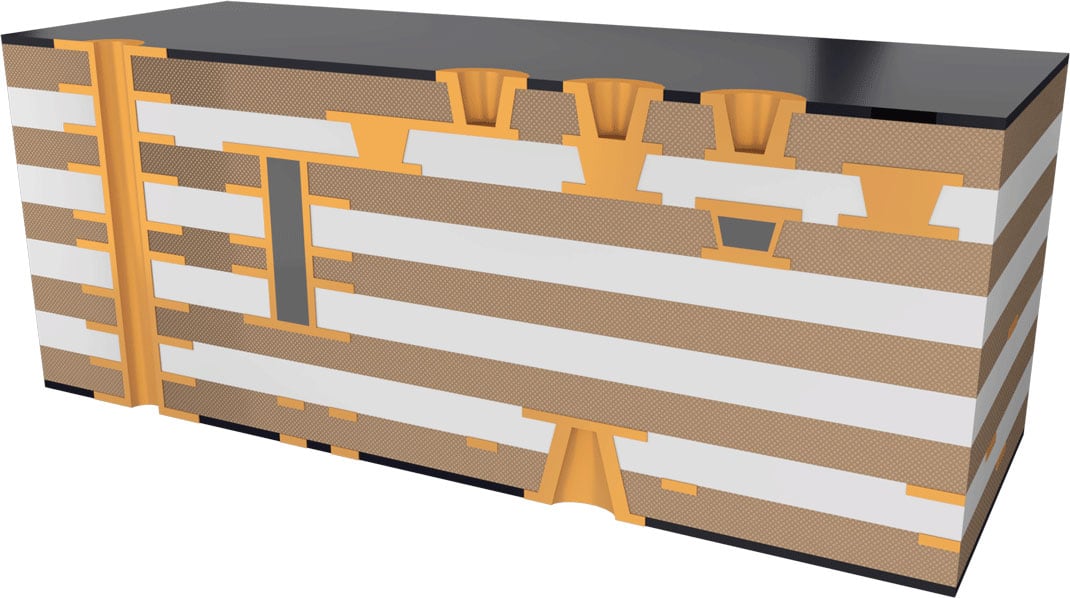

Rigid-Flex

With the increasing demand for compact electronics, the Allegro X Design platform provides a comprehensive suite of features specifically catered for flex and rigid-flex designs. It includes robust tools for managing stack-up by zones, overlapping zones (book binding), bend areas, inter-layer checks, design rule checks (DRCs), and 3D visualization. DRCs ensure compliance with manufacturing and performance requirements. One aspect of that is the ability to check the bend radius of flexible circuits to prevent damage during flexing. Inter-layer checks help maintain consistency between multiple layers of a flex circuit, enhancing design reliability. Advanced 3D visualization tools allow designers to accurately verify flex regions during bending to resolve any issues early on, while seamless integration with mechanical CAD systems facilitates co-design and verification of electronics and enclosures, ensuring proper form and fit to avoiding late-stage changes. Utilize these capabilities to enable the creation of compact, lightweight, and high-performance PCBs that are essential in modern electronic applications.

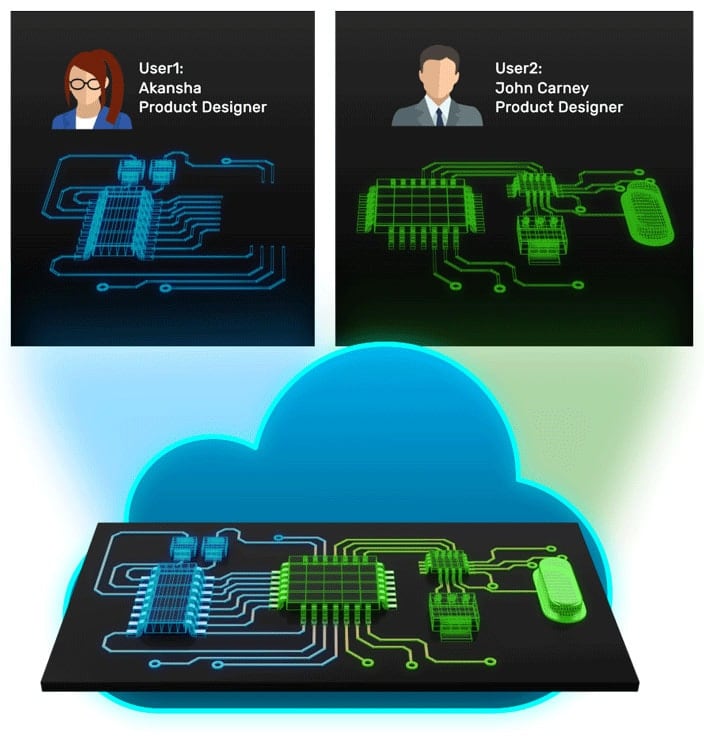

Team Design

The Allegro X Design Platform focuses on collaboration right from the start. Streamline your schematic and PCB design process by having multiple engineers and designers work simultaneously on the same project from anywhere around the globe. Real-time synchronization, version control, and conflict resolution allow you to easily maintain design integrity and prevent errors while you work in parallel with your teammates. On the schematic side, read/write permissions and locking allow for the management and partitioning of specific sections, blocks, and pages of your schematic to avoid overwriting of simultaneous changes. While on the layout side, Allegro X Symphony provides a real time collaborative environment allowing multiple designers to concurrently work on the same PCB database. No special hardware or IT support is required, and it's invoked through a simple share and invite model. This allows you to multiply your team’s effectiveness by dividing tasks such as component placement, routing, constraint assignment, integrated design analysis checking, and more, to ensure that complex designs are completed faster and with higher accuracy.

Constraint Management

The constraint management system is an integrated spreadsheet-based interface within the Schematic and PCB Editor that drives electrical rule sets, placement, routing, and manufacturing processes of your layout, ensuring accuracy and compliance with design and performance specifications. Users can define, manage, and validate multiple rules from spacing to manufacturing in a hierarchical manner. Electrical and physical rules that are created and set within the spreadsheet, dynamically update the statuses of nets based on the current state of your design to indicate whether they pass (highlighted in green) or fail (highlighted in red). This allows designers to identify and resolve any issues to optimize the design. Rules can be exported and imported, in the form of a technology file, for easy reuse across designs and technology types.

Miniaturization and HDI Design

With support for high density interconnect (HDI) and miniaturization technologies, placing embedded components, microvias, stacked vias, and blind and buried vias, is simple and powerful within the Allegro X Design Platform leading to optimized signal routing for smaller form factors. The optimized 3DX engine provides a detailed view of your HDI design so you can accurately assess the spatial positioning between components, vias and traces. Utilize the constraint manager to create miniaturization rules for optimal form factor, via spacing, and pin spacing. The robust design rule checks ensure manufacturability and reliability even in the most complex HDI designs, allowing you to create compact, high-performance PCBs for modern electronics.

MCAD Collaboration

The integrated ECAD-MCAD capabilities between Allegro X PCB Editor and Mechanical CAD (MCAD) tools such as Autodesk Fusion, Dassault Systèmes SOLIDWORKS and CATIA, Siemens NX, and PTC Creo, foster an efficient and collaborative environment between electrical and mechanical design teams. Incremental data exchange (IDX) technology is used as the bi-directional pathway to accept, reject, and revert changes, allowing both teams to stay up to date with design modifications and work on the latest design iteration. The co-design solution enables 3D visualization as well as the effective management of critical design elements such as component placement, routing, and mechanical enclosures, so that your design meets manufacturing as well as first-pass form and fit checks.

SPICE Simulation

PSpice is natively integrated within Allegro X System Capture, allowing engineers to perform detailed analysis of analog and mixed-signal designs right within the design environment without having to duplicate efforts re-drawing a schematic in a simulation only tool. With direct access to over 35,000 parametrized models and libraries, it’s easy to select reliable components and ensure accurate simulations. Maximize circuit performance, reliability, and cost-effectiveness with access to a wide range of simulation and analyses, such as DC, AC, transient, parametric sweep, Monte Carlo, sensitivity, electrical overstress (EOS), and circuit optimizer.

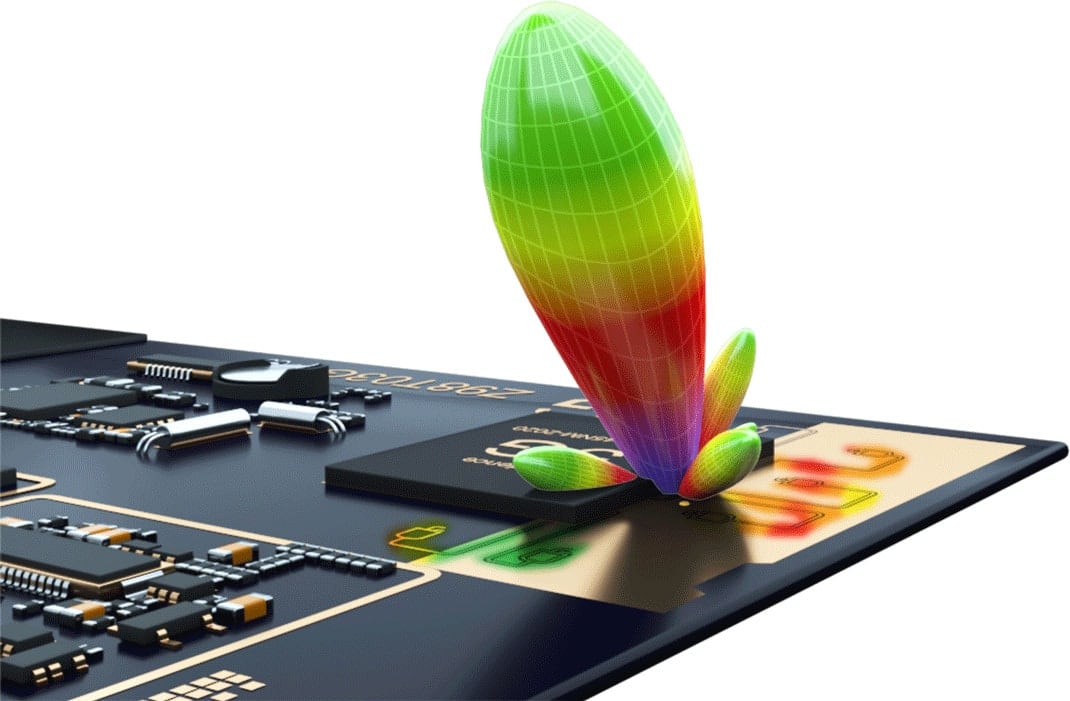

RF Design and Analysis

The advanced tools within the Allegro X Design Platform provide designers with comprehensive solutions to tackle the unique challenges of high-frequency circuit design. These tools enable precise modeling and simulation of RF components, ensuring signal integrity and optimal performance in complex Radio Frequency (RF) environments. RF structures created in AWR Microwave Office can be imported seamlessly within Allegro X System Capture, reducing time for translation and potential errors. Access features like RF schematic design and editing, shape-based routing, any-angle layout, automatic layout vs. schematic (LVS) verification, and an integrated 3D field solver for accurate parasitic extraction. Simulation support for both time and frequency domain facilitates exhaustive testing and validation of RF designs before manufacturing, ensuring the final product aligns with all performance specifications.

成功案例

成功案例