时间:2023-08-10

时间:2023-08-10

作者:Xinqiao

作者:Xinqiao

阅读 6008次

阅读 6008次

目前,Cadence SPB产品已发布至 SPB 22.1版本。在这一版本中,Allegro PCB 部分除了性能和显示功能持续提升外,高速结构设计相关功能也再增强,如参数化高速过孔功能、支持结构替换差分对过孔,并增加Shape过孔和引脚转换、优化尺寸标注功能、走线禁止区例外使用模型等优化设计效率相关功能,这些增强功能,我们将在接下来陆续与大家分享。

OrCAD Capture和OrCAD Capture CIS 22.1

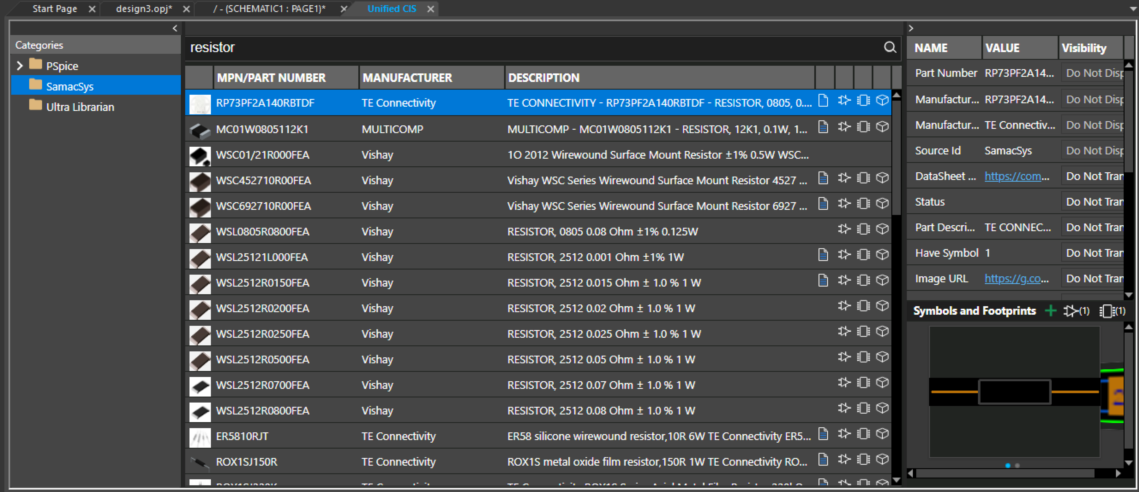

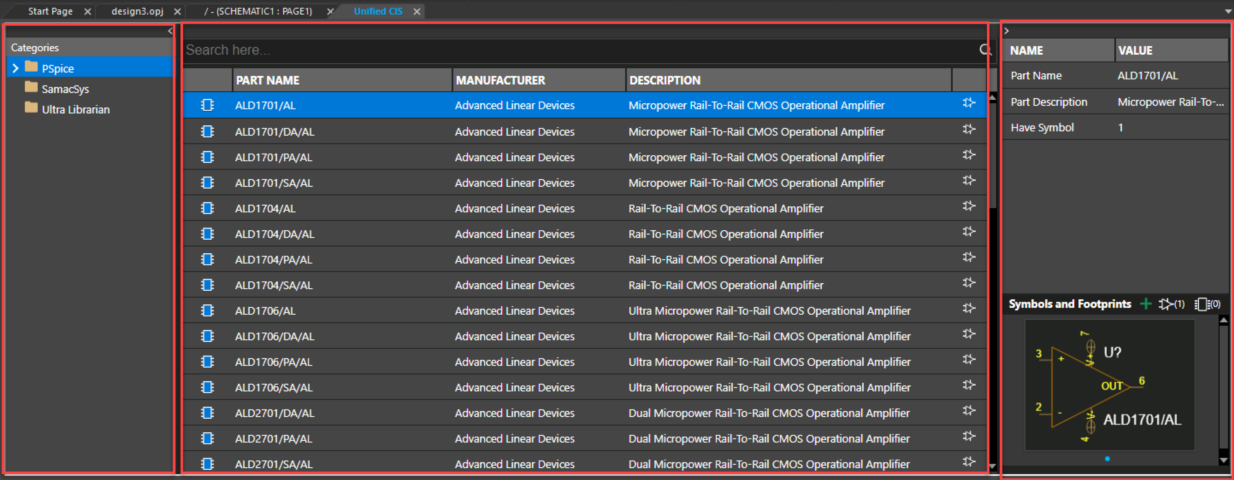

在OrCAD Capture和OrCAD Capture CIS 22.1中,增加了Unified Component Information System (CIS)功能。

Unified Component Information System (CIS)

Unified CIS是一个组件管理系统,它提供了一个直观的用户界面来访问来自各种来源的组件,而无需额外创建首选零件数据库和设置ODBC数据源。

在Unified CIS界面,您可以从以下来源查看、搜索和放置OrCAD Capture设计中的组件:

● Cadence提供的PSpice libraries

● Cadence支持的外部内容提供商 – SamacSys 和 Ultra Librarian

从Unified CIS界面访问以下功能:

● 查看组件及其属性

● 查看符号和示意图

● 在原理图上放置元件

从Categories浏览器(左窗格)中选择源。在增强型零件浏览器(中间窗格)中查看来自不同来源的零部件的详细信息。在properties浏览器(右窗格)中查看组件的属性详细信息。

PSpice and PSpice Advanced Analysis

以下介绍22.1版PSpice和PSpice Advanced Analysis中的增强功能和新功能。

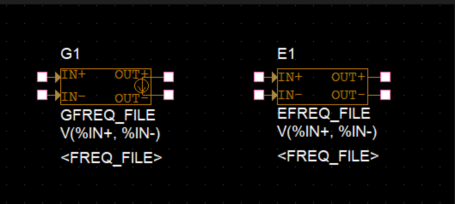

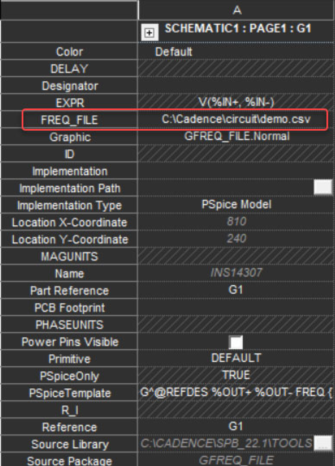

1、使用Behavioral Sources 创建 Frequency-Based 的阻抗

22.1版提供了一种方便的方式,使用CSV格式的频率表实现随频率变化的阻抗。为支持此功能,将两个新组件GFREQ_FILE和EFREQ_FILE添加到Cadence库abm.olb中,可从以下位置获得:/tools/capture/library/pspice/abm.olb

要在设计中使用组件,请将abm.olb中的GREQ_FILE或EFREQ_FILE放置在画布上。

然后,可以为放置的一个组件打开 Property Editor,并在FREQ_file属性的值字段中指定CSV文件的路径,如下图所示:

2、支持Digital Clock Source的表达方式

PSpice® Modeling Application中对表达式的支持现已扩展到digital clock source, DigClock.

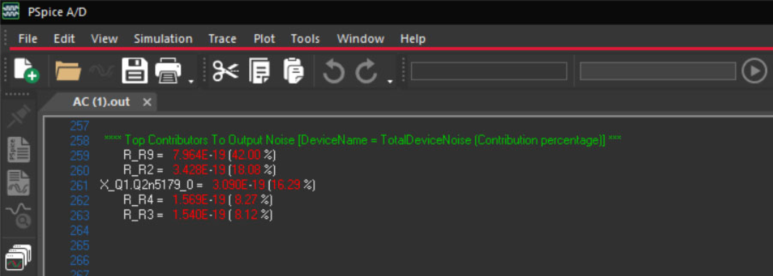

3、噪声分析输出功能的增强

现在可以使用PRINT_NOISE_DISTRIBUTION选项为噪声分析报告设置较高noise contributors 的数量。

例如,要报告前7个noise contributors,请使用以下语法:

.OPTIONS PRINT_NOISE_DISTRIBUTION =7

默认情况下,只报告前5个noise contributors。

如果设备的数量小于高noise contributors的数量,则输出所有设备的noise contributors。

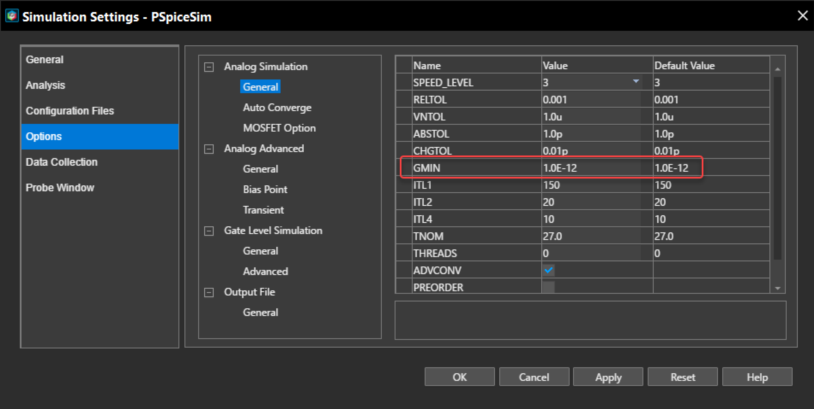

4、零值电阻的增强

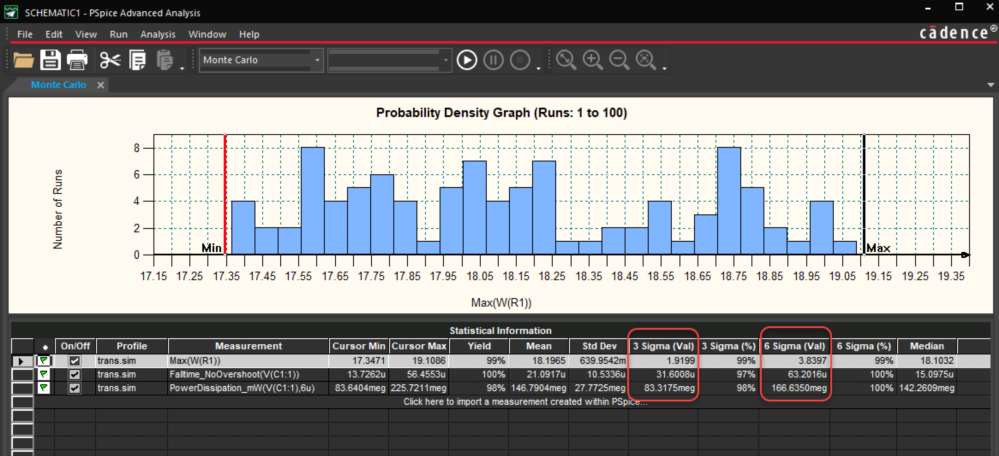

5、蒙特卡罗分析

Monte Carlo分析增强,可以计算和报告 3-Sigma和6-Sigma值。

Sigma值在 Monte Carlo统计结果网格中显示为列。

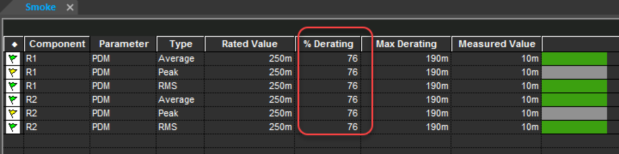

6、Smoke分析中的增强功能

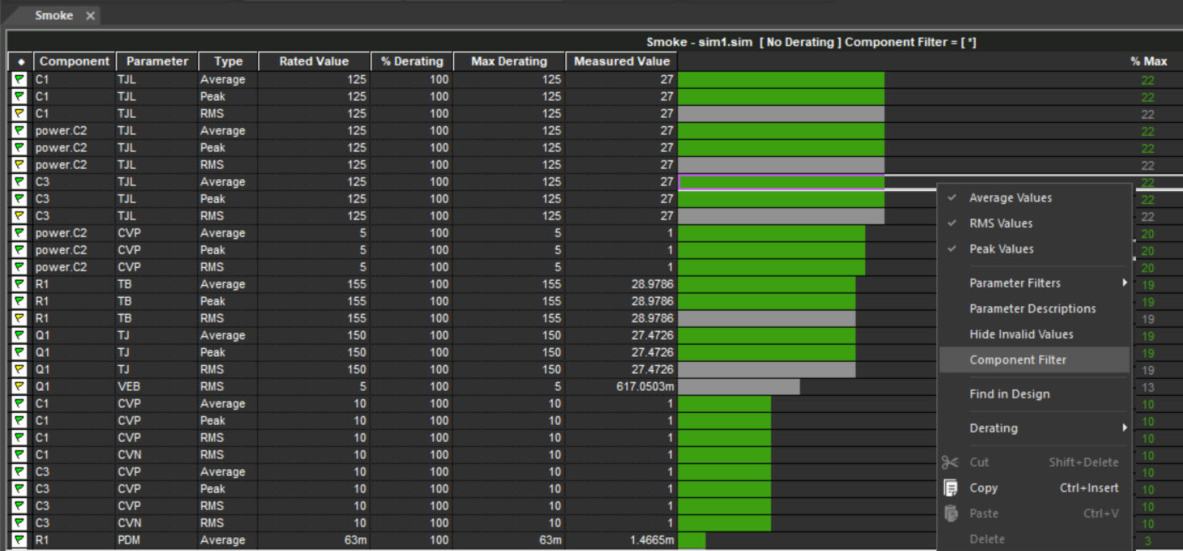

使用Smoke分析,您可以在Smoke结果中启用功率自动降额和分层组件过滤。

■ 现在可以通过使用星号来匹配字符串后面或前面的任何模式来过滤分层组件。要搜索零部件,请使用Component Filter 快捷命令。

例如,要显示POWER模块中的所有电阻器,请右键单击组件,然后在Smoke Analysis窗口中选择Component Filter。然后,您可以指定*.C2或*Power.C2来匹配Power模块中的所有电容器。

过滤后的组件显示在Smoke Analysis窗口中。

Cadence SPB 22.1新版本中的许多功能都更加人性化、智能化,同时更符合设计人员的需求;另外,模块复用也越来越普遍,符合设计要求的查询也经常出现在设计的 Layout 中。

Allegro®PCB Editor和Allegro™Package Designer Plus 22.1

Allegro®PCB Editor和Allegro™Package Designer Plus 22.1版中的新功能和增强功能,如果某个功能仅在一个Layout编辑器中可用,或针对特定许可证,我们会标记注释。

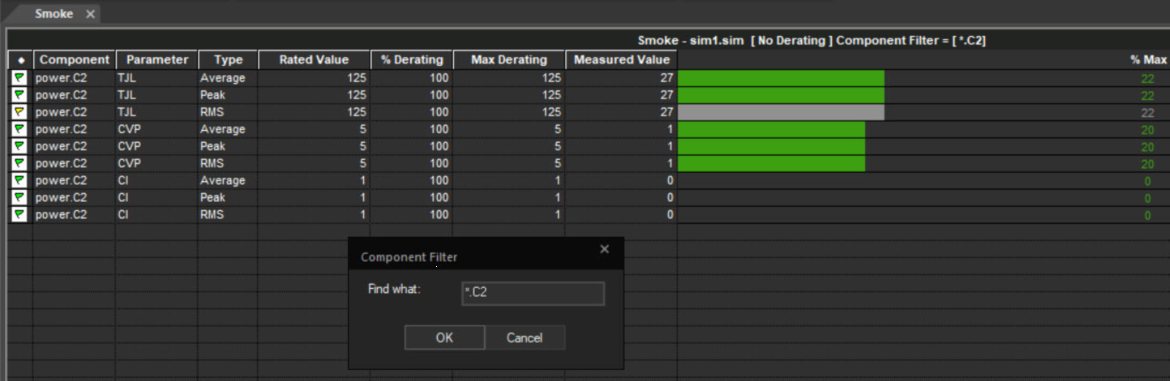

// 形状(Shape)、过孔和引脚的转换 //

将GERBER或DFX档转换为智能设计时,有时需要将这些档转换为不同的设计对象以建立连接。例如,有时导入的是铜箔但是我们需要的却是过孔和Pin脚,或者需要的是电气连接线但导入的却是非电气的连接线。另一种设计是基于电气线、非电气线和引脚或过孔焊盘自动生成铜箔的形状,而不是手动来画。

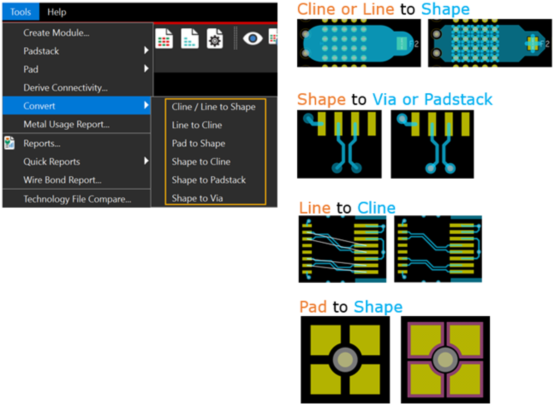

// 尺寸标注功能更新 //

“Dimension Environment ”命令提供了在设计中对象之间的关联标注。因此,当移动或改变其中一个标注对象时,会自动更新标注结果。尽管标注结果的自动更新很有用,但标注环境下的删除或修改标注结果可能是一项繁琐的任务。此外,非关联标注是锁定的,只能通过删除,再生成来更新。即使是微小的调整也需要通过删除和重新生成等一系列繁杂的操作来完成。

在此版本中,您可以将标注分离到各个独立对象中,这样就可以对标注进行更改,且无需删除和重新生成标注。若要将标注打散成不关联的对象,请选择“Manufacture”–“Dimension Environment”,然后选择“Disband dimensions”命令。该命令既可以用于关联标注,也可以用于非关联标注。

// 走线禁止区例外使用模型的增强 //

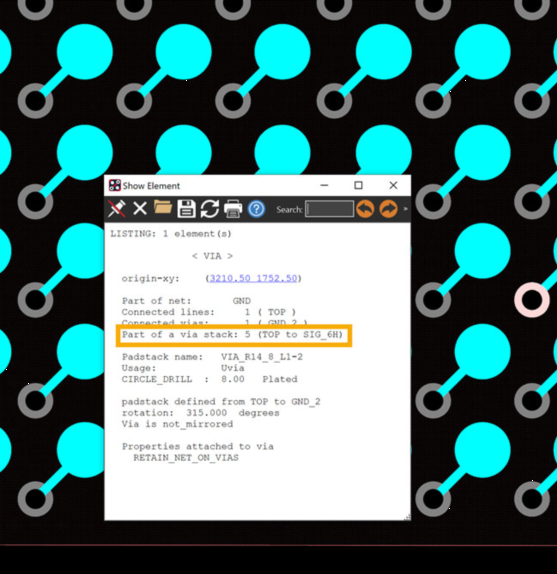

尽管过孔堆栈在当今的设计中很常见,但它们不能用于设计的某些领域。当然,您可以通过过孔列表的区域规则来检查,但这可能会导致一些复杂的假性DRC错误。

可以通过在走线禁止区的Shape上添加VIA_STACKING_NOT_ALLOWED属性的方式,来检查此区域内堆栈过孔的位置并标识出DRC。设定此属性的同时,再设定VIA_ALLOWED属性,如此,在此禁止区内可以打过孔但如果存在过孔堆栈就会有DRC。

// 性 能 优 化 //

22.1版中在加快设计时间方面进行了增强。此版本中的一些主要性能改进如下:

● 在具有大量DRC的设计中具有更好的性能

● Smooth更新更快

● 更好的移动处理性能

● 限制命令窗口消息

● 负片层的快速DRC检查

1、在具有大量DRC的设计中具有更好的性能

现在,具有大量DRC的设计处理速度更快。例如,对于需要查询或删除DRC的命令,提高了450倍。导致DRC变更的任务(例如批量添加或移动对象、或更新Shape),现在处理起来也更快。

2、更新至Smooth状态更快

由于新的PolyBool引擎和形状修剪工作的改进,“Update to Smooth”命令现在明显变得更快。例如,在某些情况下,运行“Update to Smooth”命令所需的时间已从一小时减少到约2分钟。

3、更好的移动处理

移动大型模块或大型复杂结构,现在的速度更快。例如,移动大型模块所需的时间减少了19倍,用时只需要5秒,而不是之前的82秒。同样,移动一个耗时18分钟的复杂结构,现在只需1.2分钟。

4、每层形状参数覆盖的性能更好

当使用“Dynamic Shape Layer Parameters”对话框设定参数时,各种命令(如:Add Connect, Slide, Move,和 Structure Redefine.)的性能都有所提高。

5、限制命令窗口消息

设计任务的非关键消息在“命令”窗口中不再可见。例如,在较早版本中,通常在执行大型操作时,会显示1000多条消息在命令窗口中。现在,最多限制为100条。

6、更快的负片层DRC检查

在此版本中,负片层DRC性能有所提高。例如, Negative Island的检查现在快了20倍。

// 显示器增强功能 //

在这个版本中,显示器得到了增强,对复杂高密度设计方面进行了简化。以下部分介绍了显示增强功能:

● 支持扩展的GPU

● 高分辨率显示器的标准化格式

1、支持扩展的GPU

注:此功能仅适用于Allegro X Venture Layout产品。

在这个版本中,除了对NVIDIA GPU的现有支持外,也能支持Intel和AMD的整合GPU。具体有以下增强功能:

● 平移和缩放的性能提高

● 增强了显示质量:虚拟机需要专用或整合的NVIDIA、Intel或AMD物理GPU。

● 启动布局编辑器时,会自动检测并启用较佳GPU:

○ 要禁用GPU 画布,请在“User Preferences”设置中设置disable_GPU变

○ 要禁用会话的GPU画布,请使用“–nogpu“开关(如:allegro–nogpu)

注意:这个功能处于试用阶段。必须启用以下环境变量才能正常使用新的GPU 画布:

set PG_PLUGIN_PATH $ALLEGRO_INSTALL_ROOT/tools/plugins/gpu.

2、高分辨率显示器的标准化格式

具有4K或更高分辨率的高分辨率的显示设备使用显示缩放来提高显示可见性。然而,由于缩放,画面显示的某些部分被截断。现在,您可以通过指定缩放系数来实现窗口的正常显示,避免了因显示缩放而造成画面显示不全的问题。

在此版本中,使用系统变量ALLEGRO_HIGH_DPI_ENABLED=1,来实现缩放系数为1.25,以确保窗口的正常显示。

图片中右侧的图像为按1.25倍的比例缩放:

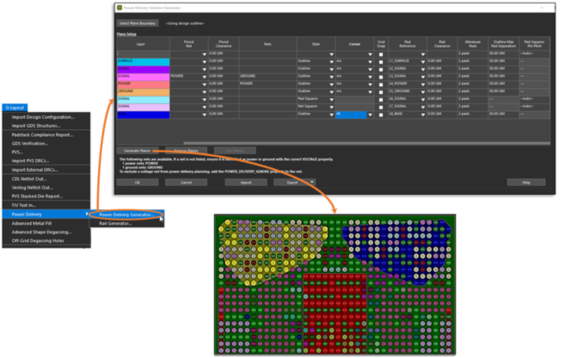

// Power Delivery Generator(供电平面产生器) //

注:此功能仅适用于具有Silicon Layout选项的Allegro Package Designer Plus产品。

使用Power Delivery Generator,可以依据布局中Pin脚所在位置创建平面区域。可以根据布局上突出显示电源网络以查找群集,然后改为运行此工具,而不用手动定义区域。

Power Delivery Plane Generator(Si Layout – Power Delivery – Power Delivery Generator)功能根据目标区域内的引脚(Pin)或过孔(vias)的位置创建电源平面和地平面。

Outline - Region defined by a bounding shape, convex_hull

平面层边界可以是用来填充平面内空余空间的网络形成的外边沿,也可以是引脚组所构成的凸形区域,或者是芯片电源域内引脚簇构成的矩形区域。

注: 您只能选择具有Ratsnest Schedule和Voltage属性的电源网络和地网络。可以在设计过程中继续更改参数,并根据需要重新生成所有平面。

Allegro®System Capture

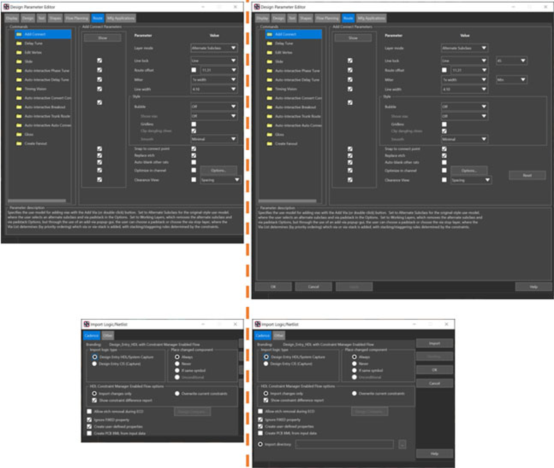

接下来将介绍的是22.1版Allegro®System Capture的增强功能和新功能。主要包括:加速原理图设计、Variants流程、系统级设计增强、支持导入.MCM文件 、Library Authoring增强功能、设计完整性中新的审计规则、使用Tcl和Directives进行定制。

在处理原理图设计时可以用来提高工作效率的新功能和增强功能。

1、性能优化

在本版本中,对原理图设计的许多方面进行了改进,以提高性能和响应时间,包括以下方面:

■ 打开和保存设计

磁盘上的System Capture设计和库数据现在使用行业标准的压缩-解压缩方法。这使得项目打开、保存、归档和其他相关磁盘IO操作的性能提高了2倍到5倍。

■ 布线性能

交互式布线性能已提高了2倍至5倍,采用了新的结点计算实时算法和改进的数据缓存技术。

■ 画布选择

对于大型原理图中选择操作的性能也提高了3倍至5倍

2、显示基础网络标记

当多个网络出现别名时,获胜的网络名称将用作物理名称。现在System Capture可以配置在画布上显示获胜的网络或基本的网络。例如,在下图中,DELTA是基础网络。您在网络名称旁边看到的后缀称为文本覆盖,可以自定义。

3、扩展物理网名的前缀和后缀

在阶层设计中放置模块时,可以为模块选择一个前缀或后缀。此前缀或后缀现在也应用于单个网络或总线的物理网名称。此功能不需要额外设置。下图分别显示了设置前缀和后缀的效果。

4、支持模块打印

默认情况下,将打印设计中的所有模块和页面。要限制某些模块的打印,请将site.cpm或design文件中的 PRINT_EXCLUSION 指令设置为PRINT_EXCLUSION 'true'

5、支持页面边框上的属性

6、以只读方式

信息推荐

信息推荐