Sigrity SPEED2000 ERC

电气规则检查(ERC)是一种快速而简单的方法,可在不需IBIS模型的情况下,扫描整个电路板以查找一阶电气设计问题。其填补了基于几何结构的设计规则检查(DRC)和使用IBIS模型执行的基于仿真的验证仿真任务之间的空白。

基础ERC

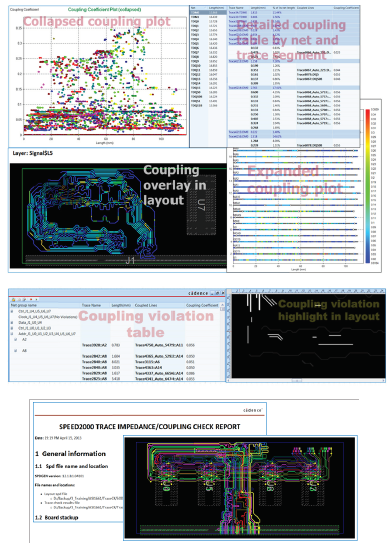

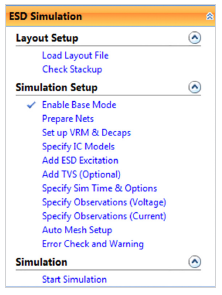

迹线阻抗、耦合和返回路径的间断性检查为布局迹线属性提供了微观视角,对设计和排错很有帮助。通过该技术,用户可以快速筛选电路板布局,以获得:

按网络列出的阻抗和耦合结果的高级概要,包括过孔数量、返回路径间断性数量以及空隙上的迹线部分数量、迹线长度和迹线延迟

按迹线段进行详细/交互式检查,包括折叠和扩展绘图、布局叠加、和交叉探测布局绘图

单端和差分阻抗以及耦合

基于用户定义的阈值,错误报告将格式化至表格中,并能够在布局中高亮显示

迹线检查结果附于网络组中,使得对照变得简单且直观。网络组的设置简单且自动化。根据迹线检查结果,用户可以非常容易地看到阻抗/耦合的分布,以识别绘图中错误情况,并使用交叉探测来定位布局中的错误,报告格式为HTML。

图1 跟踪耦合检查结果示例

基于仿真的ERC

基于仿真的规则检查提供了对总体SI性能更细致的视角,这对在开展细致化的功率监测SI分析进行验证之前,进行额外的筛选和设计审查具有很大的帮助。基于仿真的电气规则检查依赖于时域仿真,该仿真考虑到串扰和非理想电源和接地电源,而无需分配IBIS模型。通过易于使用的工作流程以及高级的自动化并行计算,在检查大量网络时节省时间。生成的结果包括:

TX/RX波形和最坏情况下的NEXT/FEXT波形

基于接收器处的信号幅度、元件间干扰(ISI)和串扰的SI性能指标

前十串扰干扰源

广泛的检查报告

基于仿真的电气规则检查可用于以下情况:

筛选电路板并确定最坏情况以进行进一步分析

调查违反设计规则和权衡对SI的影响

与已知的良好设计或参考设计进行比较

功率监测ERC

当使用非理想PDN运行时,可以扩展基于仿真的规则检查,以模拟电源干扰的影响和对信号的耦合。这些扩展检查包括:

与信号阻抗间断性反射耦合的水平振荡

与产生新串扰的信号耦合的水平振荡

增加耦合信号之间串扰的水平振荡

由电源或接地水平干扰影响的延迟

通过耦合到电源和/或接地水平信号的影响,导致影响反射和串扰结果的振荡

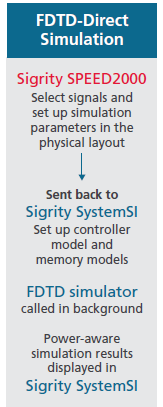

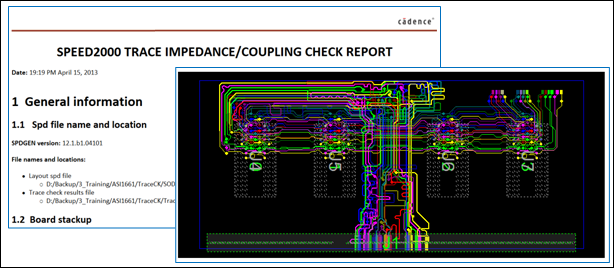

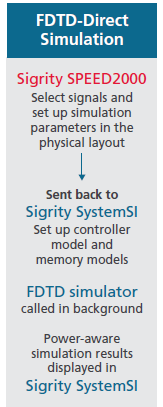

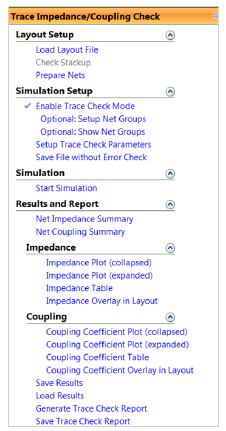

通过Sigrity SPEED2000和System SI工具进行DDR仿真

由于DDR仿真设置以及对仿真后结果解译的复杂性,Cadence建议使用Sigrity SystemSI来执行DDR仿真。Sigrity SPEED2000在从初始反射仿真过渡到包含同步整流干扰影响的验证级功率监测仿真方面发挥着重要作用。通过使用Sigrity SPEED2000工作流程所创建的提取SPICE模型,可由Sigrity SystemSI执行初始仿真。对于最终验证,Sigrity SystemSI中相同的用户界面可用于执行Sigrity SPEED2000 FDTD-direct工作流,其包含信号、电源和接地之间的交互作用。

图2 使用FDTD-direct仿真的功率监测DDR流程

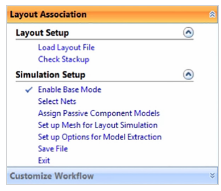

结合使用Sigrity SPEED2000和SystemSI技术,用户不需要为互连模型生成S参数模型是其一项重要优势,这样可以在SPICE时域仿真中使用S参数时避免典型的非被动和非因果问题。当仿真中包含大量DDR信号时,以及DDR电源和接地网络和大量的封装解封,这些问题通常更为明显。使用Layout Association(FDTD-direct)工作流,可以运行假设的DDR仿真以查看非理想电源/接地对内存接口设计的影响。

图3 Sigrity SPEED2000工作流程设置,用于从Sigrity SystemSI进行FDTD-direct仿真

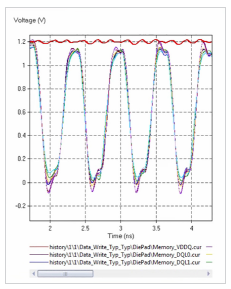

图4 带有Sigrity SPEED2000 PCB模块用于FDTD-direct仿真的Sigrity SystemSI

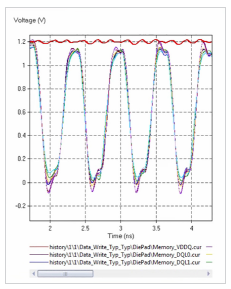

图5 FDTD-direct工作流程的功率监测仿真结果

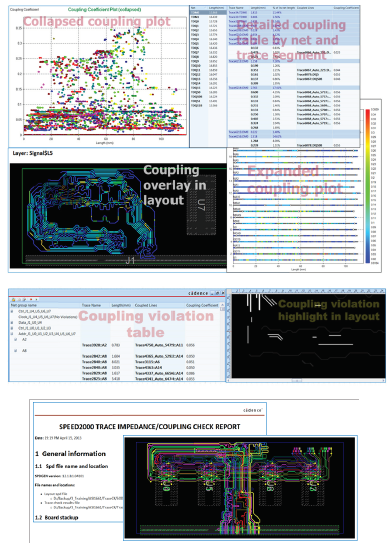

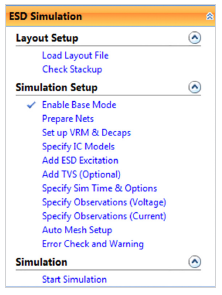

ESD工作流程

静电放电(ESD)工作流程用于测试来自外界突发且意外的电流影响,例如人体带有电荷时触碰或插入的线缆。该流程包括对静电放电枪模型位置的定义,并观察对电路板、信号、平面的影响。瞬态电压抑制(TVS)二极管及其箝位电压峰值的能力都包括在ESD模拟中。

图6 Sigrity SPEED2000 ESD仿真工作流程

使用Sigrity SPEED2000引擎作为通用SI/PI工具

Sigrity SPEED2000引擎提供了其他工作流程和功能,使其成为通用SI/PI工具:

电源-接地干扰仿真工作流程可用于I/O电源的直接时域电源/接地干扰仿真。作为Sigrity SPEED2000的工具替代方案,其可提取S参数模型并将之用于SPICE仿真。然而,由于I/O电源模型通常包含用于相同电源或接地网络的许多早期相同端口,因此使用SPICE仿真引擎在时域中运行仿真可能非常困难。通过Sigrity SPEED2000,您可以获得稳定的模拟结果。

虚拟示波器TDR/TDT工作流程是评估PCB设计中阻抗不连续性的一个方便功能。当需要评估由于基准不连续性和过孔引起的阻抗不连续性时,它尤其有用。

EMI仿真工作流程使您能够使用具有正确激励的设备模型来运行仿真,以表示EMI源。

您还会发现以下具有帮助的功能:

易用的解封管理器可以分配解封模型,其模型包括来自Kemet、Murata、Samsung、TDK、Taiyo-Yuden、以及默认的解封库。

布局编辑功能,用于对假设分析进行布局更改

时域和频域波形显示和测量

灵活的三维结果可视化,用于信号和干扰的生成和传播

布局虚拟三维漫游

通过工作流进行快速仿真设置

Sigrity SPEED2000工具使用工作流和向导来指导您快速完成设置仿真。该工具提供了六个以应用程序为中心的工作流,每个都对应于在SI/PI/EMI仿真中如何使用它的主要使用模型。

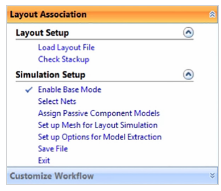

迹线阻抗/耦合检查

SI性能指标检查

PDN仿真

虚拟范围:TDR/TDT

EMI仿真

通用SI仿真

图7 迹线阻抗/耦合检查的工作流程示例

支持多种布局数据类型

Sigrity SPEED2000提供对物理设计数据直接进行时域仿真。您可以轻松使用Cadence SIP Digital Layout、Cadence Allegro® Package Designer、和Cadence Allegro PCB Designer的布局数据。而后,只需要将电路模型关联上布局中的器件即可。通过这种方式,过孔、信号迹线、电源/接地层、以及无源和IC元件电路都包含在仿真红,为您提供全面且准确的SI/PI性能结果。所有其他主要类型的布局数据库,例如Zuken和Mentor Graphics的,都可以转换到Sigrity SPEED2000。

产品详情

产品详情

成功案例

成功案例